Explain Different Vectored Interrupts of 8085

Suppose we have to calculate vector address of RST 4 then it will be. I TRAP ii RST 75 ii RST 65 iv RST 55 v INTR.

Chapter Interrupts Ppt Download

When ALE goes HIGH the latch is enabled.

. There are eight Software interrupts in 8085 Microprocessor. There are 8 software interrupts in 8085 ie. There are total 8 software interrupts present in 8085 ie from RST 0 to RST 7.

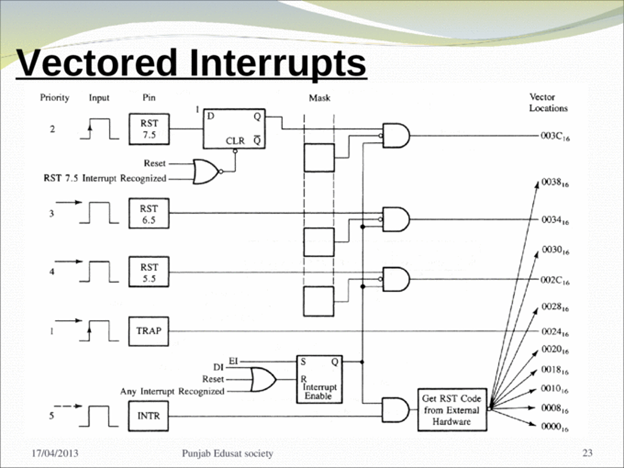

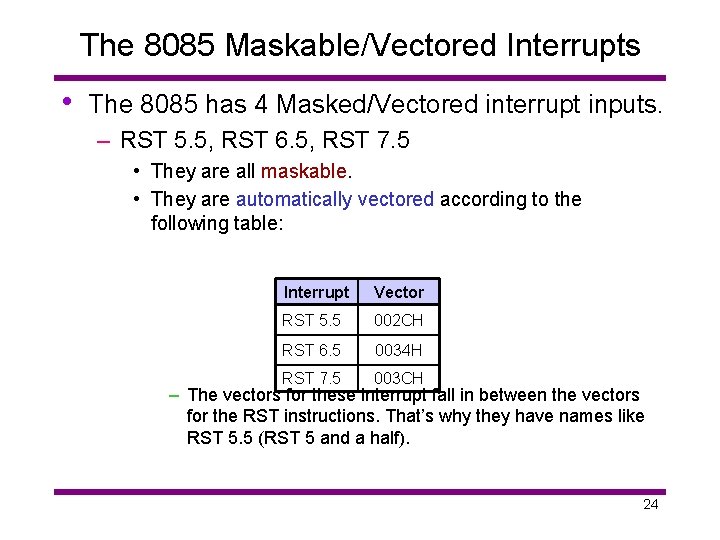

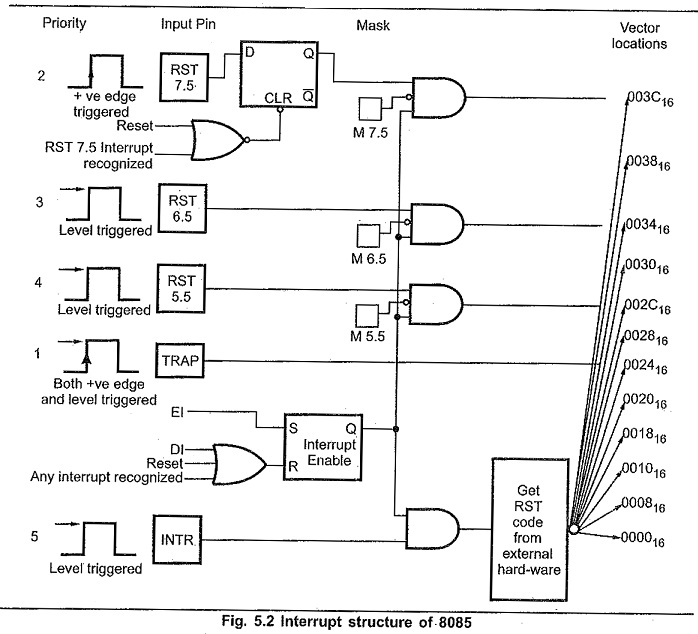

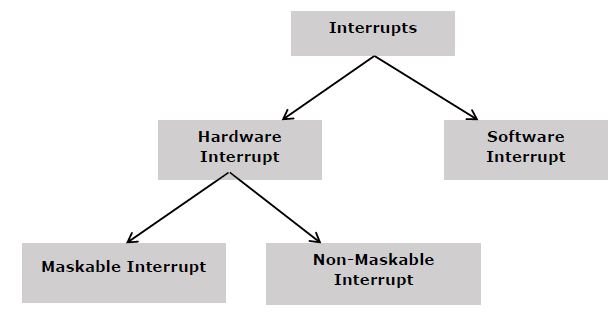

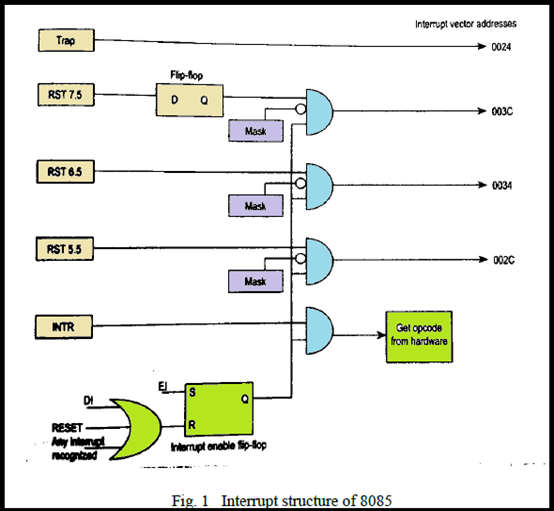

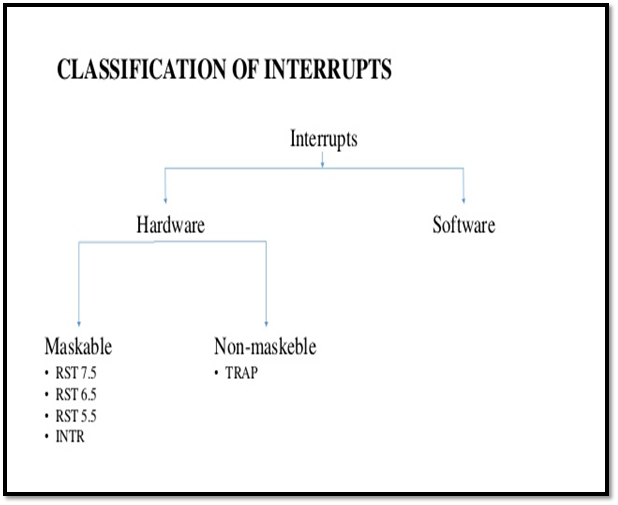

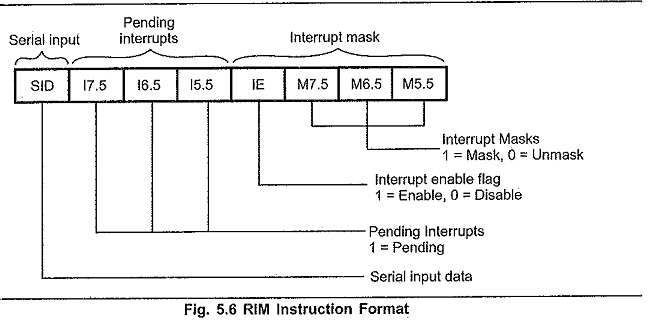

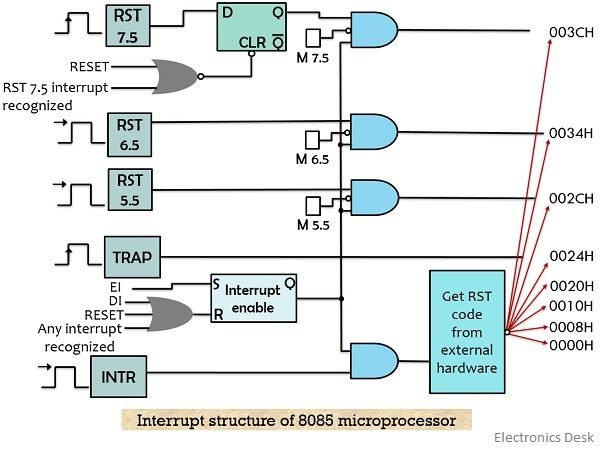

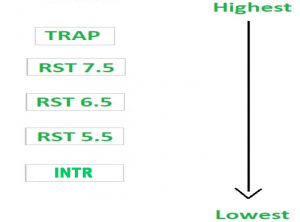

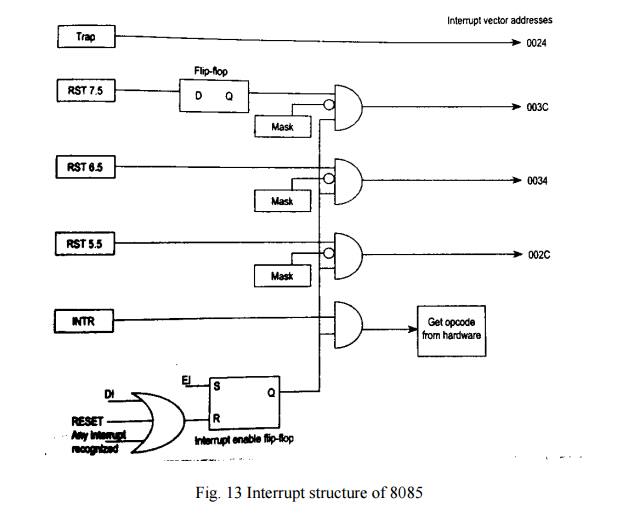

Basically whenever a software interrupt is generated then its vector address is calculated by. Up to 24 cash back The 8085 Interrupts The 8085 has 5 interrupt inputs. INTR RST 75 RST 65 RST 55 are maskable interrupts in 8085 microprocessor.

RST0 RST1 RST2 RST3 RST4 RST5 RST6 and RST7. The software interrupts cannot be masked and they cannot be disabled. 5 These interrupts may be non- maskable or maskable.

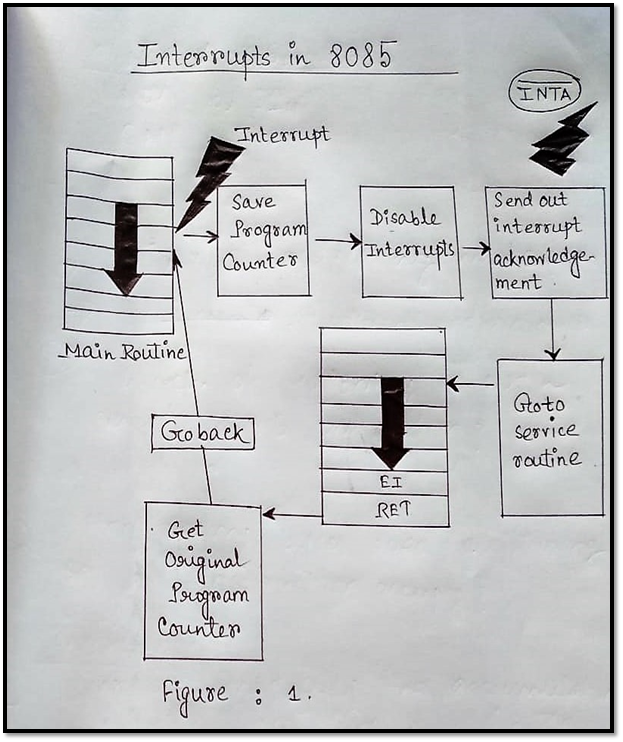

Note NTA is not an interrupt it is used by the microprocessor for sending acknowledgement. After completing the subroutine program the program control returns back to the main program. The TRAP signal must make a LOW to HIGH transition and remain HIGH until acknowledged.

The microprocessor executes either interrupt acknowledge cycle or ideal machine cycle to acknowledge this interrupt. The INTR interrupt is the only non-vectored interrupt in the Intel 8085 microprocessor. Hence the Trap line always makes a transition from 0 to 1 and remains in state 1 until the end of the execution of an instruction for the interruption of 8085.

In 8085 microprocessor there is 5 hardware interrupts. ü Interrupt number 8 vector address ü For RST 55 8 40 28H ü Vector address for interrupt RST 5 is 0028H Table 14 Vector addresses of all interrupts. Vector Address Interrupt number 8.

TRAP is a non-maskable interrupt. It is the acronym for Address Latch Enable pin number 30 used to demultiplex the multiplexed lower order addressdata bus. It means that when these interrupts are given it is directed or vectored to transfer the control to specific memory location given by.

Maskable Non-maskable interrupts Vectored Non-Vectored interrupt Maskable Non-maskable interrupts Mask means to block. Maskable and Non-Maskable Interrupts Maskable interrupts are interrupts that can be blocked. All software interrupts of 8085 microprocessors are vectored interrupts.

1 These interrupts are vectored interrupts. The microprocessor jumps to the specific service routine. Vectored interrupts require the IVA to be supplied by the external device that gives the interrupt signal.

The INTR input is the only non-vectored interrupt. Microprocessor they are known as Hardware Interrupts. The microprocessor 8085 has five hardware interrupts.

It is unaffected by any mask or interrupt enable. 8085 provides 5 hardware interrupts. 10 b Discuss the register sets in 8051 micro- controller with function of each register.

Briefly explain each of them. They are INTR RST 75 RST 65 RST 55 TRAP. PIN 11 is the interrupt acknowledgement INTA that is generated by the 8085 processor in response to the different interrupts that arrive at.

Vectored Interrupts Devices that use vectored interrupts are assigned an interrupt vector. INTR is maskable using the EIDI instruction pair. From RST0 to RST7.

Name the hardware interrupts of 8086. During T1 the ALE goes HIGH. Non-Maskable Interrupts are those which cannot be disabled or ignored by microprocessor.

TRAP has the highest priority then RST75 and. TRAP is a Non-maskable interrupt. 10 Group B 5.

The starting address of 8085 is known by itself the of the ISS as 45 8 0024H. TRAP is the only non-maskable interrupt in the 8085. They are TRAP RST 75 RST 65 RST 55 and INTR.

Lets check how you learn Interrupt Structure in 8085 microprocessor with a simple quiz. RST 55 RST 65 RST 75 are all automatically vectored. 6 They have lower priority than any software.

TRAP 458 0024H RST75 75 x 8 003C H. TRAP RST 75 RST 65 RST 55 and INTR. Then ISR interrupt service routine number to Program counter.

SOFTWARE INTERRUPTS OF 8085 The software interrupts are program instructions When the instruction is executed the processor executes an interrupt service routine stored in the vector address of the software interrupt instruction. RST 55 RST 65 and RST 75 are all maskable. RST0 RST1 RST2 RST3 RST4 RST5 RST6 RST7 They allow the microprocessor to transfer program control from the main program to the subroutine program.

8085 IC has six pins from PIN 6 to PIN 11 reserved for interrupts these are. Thus 0020H will be the vector address of RST 4. A Explain with examples different addressing modes supported by 8051 microcontroller.

Explain the functions of ALE in 8085. The vector address for these interrupts can be calculated as follows. There are 8 software interrupts in 8085 microprocessor.

When the device interrupts the CPU branches to the particular ISR. TRAP is also known as RST 45 On the basis of different characteristics interrupts are classified into different groups. A vectored-interrupt in 8085 is a TRAP.

4 After execution of these interrupts program counter is not incremented. So the op changes according to the ip data. Non-vectored interrupts have fixed IVA for ISRs of different interrupt signals.

Hardware interrupt There are 5 interrupt pins in 8085 used as hardware interrupts ie. There are 5 Hardware Interrupts in 8085 microprocessor. The 8085 has eight software interrupts from RST 0 to RST 7.

The ISR address of this interrupts is fixed and is known to CPU. A What are the resources integrated in micro- controller 8051. The input of Trap input is level sensitive and edge sensitive.

Explain the different modes of operation of a timer 8 Or b Explain the internal architecture of 8257 Direct Memory Access Controller. Hardware Interrupts The hardware interrupts in the 8085 are initiated or raised by an external device by applying an appropriate signal at the interrupt pin of the microprocessor. This is a number that identifies a particular interrupt handler.

These interrupts are requested by external device. It consists of both level as well as edge triggering and is used in critical power failure conditions. If two or more of these interrupts are active at the same time then the 8085 takes them in order of priority level.

It is a non-mask-able edge and level triggered interrupt. B Explain the 8085 Interrupts and their Vector locations. 8085 Microprocessor Active Reactive and Apparent Power Hardware Interrupts in 8085 Microprocessor.

What is meant by vectored interrupts. The software interrupts of 8085 are RSTO RST 1 RST 2 RST 3 RST4 RST 5 RST 6 and RST 7. Basically 8085 has five hardware interrupts INTR RST 55 RST 65 RST 75 and TRAP.

This technique is vectoring is implemented in number of ways. Draw the contents of the flag register of 8085. The priority levels of these interrupts shown in table.

4 8 32 20H. During T1 the op of latch is 05H. Software Interrupts are those which are inserted in between the program which means these are mnemonics of microprocessor.

TRAP RST75 RST65 RST55 INTA.

Interrupt In The 8085 Micro Processor By Utsa Ghosh Medium

8085 Interrupts 1 Interrupts Interrupt Is A Process

Types Of Interrupts In 8085 Interrupt Structure Of 8085

7 Difference Between Hardware Interrupt And Software Interrupt Viva Differences

Interrupt In The 8085 Micro Processor By Utsa Ghosh Medium

Interrupt In The 8085 Micro Processor By Utsa Ghosh Medium

Interrupt Structure Of The 8085

Masking Of Interrupts In 8085 Microprocessor Electronics Engineering Study Center

Interrupts In 8085 Microprocessor Geeksforgeeks

Interrupt Sources And Vector Addresses Electronics Engineering Study Center

Interrupt In The 8085 Micro Processor By Utsa Ghosh Medium

Interrupts In 8085 Microprocessor Youtube

Types Of Interrupts In 8085 Interrupt Structure Of 8085

Interrupts In 8085 Microprocessor Hardware And Software Interrupts Electronics Desk

Interrupts In 8085 Microprocessor Geeksforgeeks

Interrupts In 8085 Microprocessor Geeksforgeeks

Interrupts In 8085 Microprocessor Hardware And Software Interrupts Electronics Desk

Comments

Post a Comment